- 您现在的位置:买卖IC网 > Sheet目录3875 > PIC18F44J10-I/ML (Microchip Technology)IC PIC MCU FLASH 8KX16 44QFN

PIC16F8X

1998 Microchip Technology Inc.

DS30430C-page 43

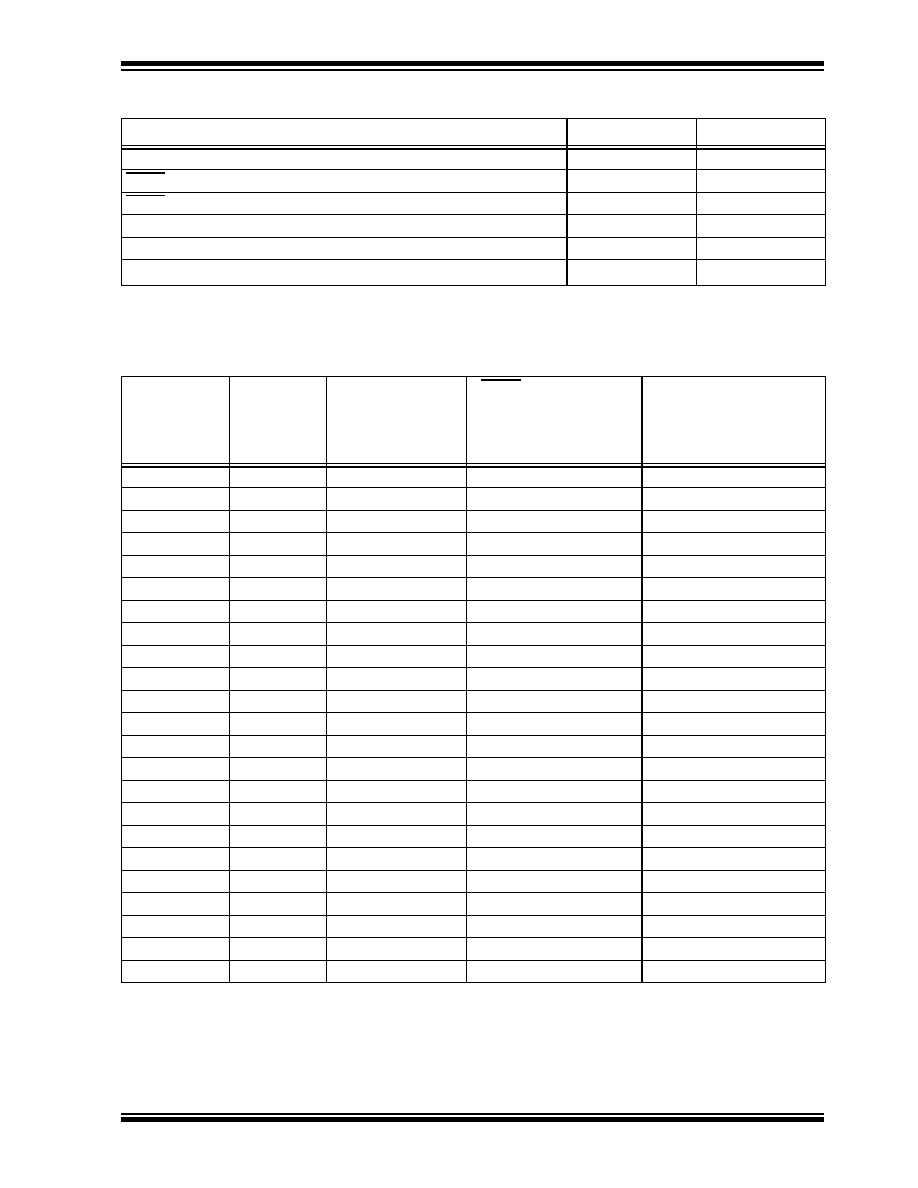

TABLE 8-3

RESET CONDITION FOR PROGRAM COUNTER AND THE STATUS REGISTER

Condition

Program Counter

STATUS Register

Power-on Reset

000h

0001 1xxx

MCLR Reset during normal operation

000h

000u uuuu

MCLR Reset during SLEEP

000h

0001 0uuu

WDT Reset (during normal operation)

000h

0000 1uuu

WDT Wake-up

PC + 1

uuu0 0uuu

Interrupt wake-up from SLEEP

PC + 1 (1)

uuu1 0uuu

Legend: u = unchanged, x = unknown.

Note 1: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector

(0004h).

TABLE 8-4

RESET CONDITIONS FOR ALL REGISTERS

Register

Address

Power-on Reset

MCLR Reset during:

– normal operation

– SLEEP

WDT Reset during nor-

mal operation

Wake-up from SLEEP:

– through interrupt

– through WDT Time-out

W

—

xxxx xxxx

uuuu uuuu

INDF

00h

---- ----

TMR0

01h

xxxx xxxx

uuuu uuuu

PCL

02h

0000h

PC + 1

(2)

STATUS

03h

0001 1xxx

000q quuu

(3)

uuuq quuu

(3)

FSR

04h

xxxx xxxx

uuuu uuuu

PORTA

05h

---x xxxx

---u uuuu

PORTB

06h

xxxx xxxx

uuuu uuuu

EEDATA

08h

xxxx xxxx

uuuu uuuu

EEADR

09h

xxxx xxxx

uuuu uuuu

PCLATH

0Ah

---0 0000

---u uuuu

INTCON

0Bh

0000 000x

0000 000u

uuuu uuuu

(1)

INDF

80h

---- ----

OPTION_REG

81h

1111 1111

uuuu uuuu

PCL

82h

0000h

PC + 1

STATUS

83h

0001 1xxx

000q quuu

(3)

uuuq quuu

(3)

FSR

84h

xxxx xxxx

uuuu uuuu

TRISA

85h

---1 1111

---u uuuu

TRISB

86h

1111 1111

uuuu uuuu

EECON1

88h

---0 x000

---0 q000

---0 uuuu

EECON2

89h

---- ----

PCLATH

8Ah

---0 0000

---u uuuu

INTCON

8Bh

0000 000x

0000 000u

uuuu uuuu

(1)

Legend: u = unchanged,

x

= unknown,

-

= unimplemented bit read as '0',

q

= value depends on condition.

Note 1: One or more bits in INTCON will be affected (to cause wake-up).

2: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector

(0004h).

3: Table 8-3 lists the reset value for each specific condition.

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

PIC16F628A-I/P

IC MCU FLASH 2KX14 EEPROM 18DIP

PIC18F24K22-I/SO

IC PIC MCU 16KB FLASH 28SOIC

PIC18F23K22-I/SP

IC PIC MCU 8KB FLASH 28SPDIP

PIC18LF23K22-I/SP

IC PIC MCU 8KB FLASH 28SPDIP

PIC24F08KA102-I/SS

IC PIC MCU FLASH 8K 28-SSOP

PIC16C58B-20/SO

IC MCU OTP 2KX12 18SOIC

PIC12C672-04/SM

IC MCU OTP 2KX14 A/D 8-SOIJ

PIC18F25K20-E/SS

IC PIC MCU FLASH 16KX16 28-SSOP

相关代理商/技术参数

PIC18F44J10-I/P

功能描述:8位微控制器 -MCU 16 KB FL 1024 RAM RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F44J10-I/PT

功能描述:8位微控制器 -MCU 16 KB FL 1 KB RAM RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F44J10T-I/ML

功能描述:8位微控制器 -MCU 16 KB FL 1024 RAM RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F44J10T-I/PT

功能描述:8位微控制器 -MCU 16 KB FL 1024 RAM RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F44J11-I/ML

功能描述:8位微控制器 -MCU 16KB Flash 4KBRAM 12MIPS nanoWatt RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F44J11-I/PT

功能描述:8位微控制器 -MCU 16KB Flash 4KBRAM 12MIPS nanoWatt RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F44J11T-I/ML

功能描述:8位微控制器 -MCU 16KB Flash 4KBRAM 12MIPS nanoWatt RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F44J11T-I/PT

功能描述:8位微控制器 -MCU 16KB Flash 4KBRAM 12MIPS nanoWatt RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT